C141-C011-01EN

# MAW3073, MAW3147, MAW3300 NP/NC SERIES

# MAX3036, MAX3073, MAX3147 NP/NC SERIES

# **DISK DRIVES**

## SCSI PHYSICAL INTERFACE SPECIFICATIONS

This Product is designed, developed and manufactured as contemplated for general use, including without limitation, general office use, personal use and household use, but is not designed, developed and manufactured as contemplated for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could lead directly to death, personal injury, severe physical damage or other loss (hereinafter "High Safety Required Use"), including without limitation, nuclear power core control, airplane control, air traffic control, mass transport operation control, life support, weapon launching control. You shall not use this Product without securing the sufficient safety required for the High Safety Required Use. If you wish to use this Product for High Safety Required Use, please consult with our sale person in charge before such use

The contents of this manual is subject to change without prior notice.

All Rights Reserved. Copyright © 2005 FUJITSU LIMITED

## FOR SAFE OPERATION

### Handling of This manual

This manual contains important information for using this product. Read thoroughly before using the product. Use this product only after thoroughly reading and understanding especially the section "Important Alert Items" in this manual. Keep this manual handy, and keep it carefully.

FUJITSU makes every effort to prevent users and bystanders from being injured or from suffering damage to their property. Use the product according to this manual.

(Proceed to the Copyright Page)

#### **Related Standards**

Specifications and functions of products covered by this manual comply with the following standards.

| Standard (Text) No. | Name                                   | Enacting Organization |

|---------------------|----------------------------------------|-----------------------|

| T10/1365D Rev 10    | Working Draft                          | American National     |

|                     | American National Standard Information | Standards Institute   |

|                     | Technology SCSI Parallel Interface 4   | (ANSI)                |

| REVISION RECORD              |                   |                  |

|------------------------------|-------------------|------------------|

| Edition                      | Date<br>published | Revised contents |

| 01                           | July, 2005        | Initial release  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

|                              |                   |                  |

| Specification No.: C141-C011 |                   |                  |

This page is intentionally left blank.

## PREFACE

This manual explains the MAW3073/MAW3147/MAW3300/MAX3036/MAX3073/MAX3147 NP/NC series 3-1/2" intelligent disk drives each having the built-in SCSI controller.

This manual details the specifications and functions of the Small Computer System Interface (SCSI) to connect the above listed disk drives to the user system. Also, the manual details various SCSI command specifications and the command processing functions, and provides the information required to creation of host system software. This manual is intended to be used by the users who have the basic knowledge of computer system operations.

The following lists the manual configuration and the contents of each chapter. The caution labels and markings are also explained.

#### **Manual Configuration and Contents**

This manual consists of the following three chapters, and the terminologies and abbreviations sections.

#### Chapter 1 SCSI Bus

This chapter describes the configuration, physical and electrical requirements, interface protocol, and other operations of the Small Computer System Interface (SCSI) which connects the MAW3073/MAW3147/MAW3300/MAX3036/MAX3073/MAX3147 NP/NC series intelligent disk drives to the user system.

#### Chapter 2 SCSI Messages

This chapter describes the type and explanation of messages defined for SCSI bus operations.

#### Chapter 3 ERROR Recovery

This chapter describes error recovery processing executed by the MAW3073/MAW3147/MAW3300/MAX3036/MAX3073/MAX3147 NP/NC series intelligent disk drives in response to various errors on the SCSI bus.

#### Glossary

This section explains the terminologies the reader must understand to read this manual.

#### Abbreviations

This section lists the abbreviated terms and their full words used in this manual.

## CONVENTIONS

This manual uses the following conventions:

NOTE: NOTE indicates the information useful for the user to operate the system.

#### **Important information**

The important information is provided with the "Important" title. The important information text is centered so that the reader can distinguish it from other manual texts. The following gives an example:

#### IMPORTANT

The IDD operates as a target (TARG) on the SCSI bus. The IDD is called "TARG" in this chapter except when clear identification is required.

#### Notations

A decimal value is indicated as it is in this manual.

A hexadecimal value is indicated in the X'17B9' or 17B9h or 17B9H notation.

A binary value is indicated in the notation similar to "010."

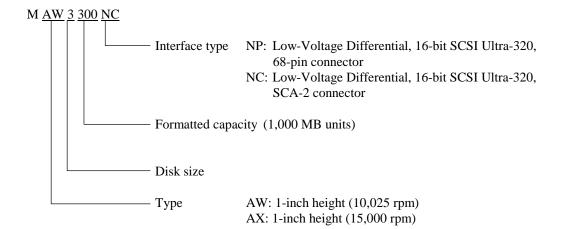

The disk drive model name has a different suffix depending on its SCSI electrical characteristics, capacity, data format used during shipment and others. The following typical model name is used except when the model needs to be distinguished. Also, the disk unit may be referred to as the "IDD" or "unit" in this manual.

#### Note 1: Model name

**Note 2:** Typical model name

| Type model name | Model name           |

|-----------------|----------------------|

| MAW3300         | MAW3300NP, MAW3300NC |

| MAW3147         | MAW3147NP, MAW3147NC |

| MAW3073         | MAW3073NP, MAW3073NC |

| MAX3147         | MAX3147NP, MAX3147NC |

| MAX3073         | MAX3073NP, MAX3073NC |

| MAX3036         | MAX3036NP, MAX3036NC |

#### **Requesting for User's Comments**

Please use the User's Comment Form attached to the end of this manual to identify user comments including error, inaccurate and misleading information of this manual. Contact to your Fujitsu representative for additional comment forms if required.

### MANUAL ORGANIZATION

| Product/<br>Maintenance Manual               | <ul> <li>General Description</li> <li>Specifications</li> <li>Data Format</li> <li>Installation Requirements</li> <li>Installation</li> <li>Diagnostics and Maintenance</li> <li>Error Analysis</li> <li>Principle of Operation</li> </ul> |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCSI Physical<br>Interface<br>Specifications | <ul> <li>SCSI Bus</li> <li>SCSI Message</li> <li>Error Recovery</li> </ul>                                                                                                                                                                 |

| SCSI Logical<br>Interface<br>Specifications  | <ul> <li>Command Processing</li> <li>Data Buffer Management</li> <li>Command Specifications</li> <li>Parameter Data Formats</li> <li>Sense Data and Error Recovery Methods</li> <li>Disk Media Management</li> </ul>                       |

## CONTENTS

| CHAP    | FER 1 SCSI BUS                                                       | 1-1  |

|---------|----------------------------------------------------------------------|------|

| 1.1     | System Configuration                                                 | 1-1  |

| 1.2     | Interface Signal Definition                                          | 1-3  |

| 1.3     | Physical Requirements                                                | 1-7  |

| 1.3.1   | Interface connector                                                  | 1-8  |

| 1.3.2   | Interface cable                                                      | 1-15 |

| 1.4     | Electrical Requirements                                              | 1-17 |

| 1.4.1   | Single-Ended type                                                    | 1-17 |

| 1.4.2   | Low-Voltage Differential type                                        | 1-20 |

| 1.4.3   | Internal terminal resistor and power supply for terminating resistor | 1-23 |

| 1.4.4   | Usage in 8-bit/16-bit transfer mode                                  | 1-25 |

| 1.4.5   | Signal driving conditions                                            | 1-26 |

| 1.5     | Timing Rule                                                          | 1-28 |

| 1.5.1   | Timing value                                                         | 1-28 |

| 1.5.2   | Measurement point                                                    | 1-42 |

| 1.6     | Bus Phases                                                           | 1-47 |

| 1.6.1   | BUS FREE phase                                                       | 1-48 |

| 1.6.2   | ARBITRATION phase                                                    | 1-49 |

| 1.6.2.1 | Normal ARBITRATION                                                   | 1-49 |

| 1.6.2.2 | QAS ARBITRATION                                                      | 1-52 |

| 1.6.3   | SELECTION phase                                                      | 1-54 |

| 1.6.4   | RESELECTION phase                                                    | 1-58 |

| 1.6.5   | INFORMATION TRANSFER phases                                          | 1-61 |

| 1.6.5.1 | Asynchronous transfer mode                                           | 1-62 |

| 1.6.5.2 | Synchronous mode                                                     | 1-65 |

| 1.6.5.3 | Paced transfer                                                       | 1-75 |

| 1.6.5.4 | Wide mode transfer (16-bit SCSI)                                     | 1-86 |

| 1.6.6   | COMMAND phase                                                        | 1-87 |

| 1.6.7   | DATA phase                                                           | 1-87 |

| 1.6.8   | STATUS phase                                                         | 1-89 |

| 1.6.9   | MESSAGE phase                                                        | 1-89 |

| 1.6.10  | Signal requirements concerning transition between bus phases         | 1-90 |

| 1.6.11  | Time monitoring feature                                              | 1-92 |

| 1.7     | Bus Conditions                                                                           | 1-93  |

|---------|------------------------------------------------------------------------------------------|-------|

| 1.7.1   | ATTENTION condition                                                                      | 1-93  |

| 1.7.2   | RESET condition                                                                          | 1-96  |

| 1.8     | Bus Phase Sequence                                                                       | 1-97  |

| 1.8.1   | Bus Phase Sequence with Information Units Disabled                                       | 1-97  |

| 1.8.2   | Phase sequences with information unit enabled                                            | 1-105 |

| 1.8.2.1 | Phase sequences for physical reconnection or selection without using attention condition | 1-105 |

| 1.8.2.2 | Phase sequences for selection using attention condition                                  | 1-106 |

| 1.9     | SPI information units                                                                    | 1-107 |

| 1.9.1   | SPI information unit overview                                                            | 1-107 |

| 1.9.2   | Information unit transfer logical operations                                             | 1-107 |

| 1.9.3   | SPI information units                                                                    | 1-113 |

| 1.9.3.1 | SPI command information unit                                                             | 1-113 |

| 1.9.3.2 | SPI L_Q information unit                                                                 | 1-116 |

| 1.9.3.3 | SPI data information unit                                                                | 1-119 |

| 1.9.3.4 | SPI data stream information unit                                                         | 1-119 |

| 1.9.3.5 | SPI status information unit                                                              | 1-121 |

| 1.10    | SCAM                                                                                     | 1-124 |

| 1.10.1  | SCAM operations                                                                          | 1-124 |

| 1.11    | Ultra SCSI                                                                               | 1-129 |

| 1.11.1  | Outline                                                                                  | 1-129 |

| 1.11.2  | Device connection                                                                        | 1-129 |

| 1.11.3  | Electrical characteristics of SCSI parallel interface                                    | 1-130 |

| 1.12    | Low-Voltage Differential                                                                 | 1-134 |

| 1.12.1  | Ultra2-SCSI                                                                              | 1-134 |

| 1.12.2  | Ultra-160                                                                                | 1-134 |

| 1.12.3  | Ultra-320                                                                                | 1-134 |

| 1.12.4  | LVD driver characteristics                                                               | 1-135 |

| 1.12.5  | LVD receiver characteristics                                                             | 1-135 |

| 1.12.6  | LVD capacitive loads                                                                     | 1-137 |

| 1.12.7  | System level requirements for LVD SCSI drivers and receivers                             | 1-138 |

| 1.13    | SCSI bus fairness                                                                        | 1-139 |

| СНАР    | TER 2 SCSI MESSAGE                                                                       | 2-1   |

| 2.1     | Message System                                                                           | 2-1   |

| 2.1.1   | Message format                                                                           | 2-1   |

| 2.1.2   | Message type                                                                             | 2-3   |

| 2.1.3  | Message protocol                                                  | 2-4    |

|--------|-------------------------------------------------------------------|--------|

| 2.2    | SCSI Pointer                                                      | 2-5    |

| 2.3    | Message Explanation                                               | 2-8    |

| 2.3.1  | TASK COMPLETE message: X'00'(T $\rightarrow$ I)                   | 2-8    |

| 2.3.2  | SAVE DATA POINTER message: $X'02'(T \rightarrow I)$               | 2-8    |

| 2.3.3  | RESTORE POINTERS message: X'03' (T $\rightarrow$ 1)               | 2-8    |

| 2.3.4  | DISCONNECT message: X'04' (T→I)                                   | 2-8    |

| 2.3.5  | INITIATOR DETECTED ERROR message: $X'05'(I \rightarrow T)$        | 2-9    |

| 2.3.6  | ABORT TASK SET message: X'06' (I→T)                               | 2-9    |

| 2.3.7  | MESSAGE REJECT message: X'07'(I↔T)                                | 2-10   |

| 2.3.8  | NO OPERATION message: X'08' (I→T)                                 | 2-10   |

| 2.3.9  | MESSAGE PARITY ERROR message: X'09' $(I \rightarrow T)$           | 2-10   |

| 2.3.10 | LINKED TASK COMPLETE message: X'0A'( $T \rightarrow I$ )          | 2-11   |

| 2.3.11 | TARGET RESET message: X'0C' (I→T)                                 | 2-11   |

| 2.3.12 | ABORT TASK message: X'0D' (I→T)                                   | 2-11   |

| 2.3.13 | CLEAR TASK SET message: X'0E'( $I \rightarrow T$ )                | 2-11   |

| 2.3.14 | CONTINUE TASK message: $X'12' (I \rightarrow T)$                  | 2-12   |

| 2.3.15 | TARGET TRANSFER DISABLE message : X'13' (I $\rightarrow$ T)       | 2-12   |

| 2.3.16 | LOGICAL UNIT RESET message : X'1C' (I→T)                          | 2-13   |

| 2.3.17 | Task attribute messages                                           | 2-13   |

| 2.3.18 | IGNORE WIDE RESIDUE message: X'23' (T $\rightarrow$ I)            | 2-14   |

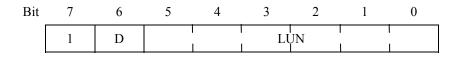

| 2.3.19 | IDENTIFY message: X'80' to X'FF' ( $I \leftrightarrow T$ )        | 2-15   |

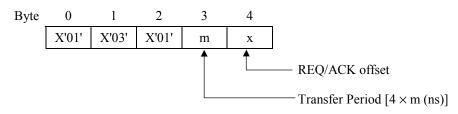

| 2.3.20 | SYNCHRONOUS DATA TRANSFER REQUEST message (I $\leftrightarrow$ T) | 2-16   |

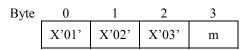

| 2.3.21 | WIDE DATA TRANSFER REQUEST message (I $\leftrightarrow$ T)        | 2-24   |

| 2.3.22 | PARALLEL PROTOCOL REQUEST message (I $\leftrightarrow$ T)         | 2-28   |

| СНАР   | TER 3 ERROR RECOVERY                                              | 3-1    |

| 3.1    | Error Conditions and Retry Procedure                              | 3-1    |

| 3.2    | Recovery Control                                                  | 3-6    |

| GLOS   | SARY                                                              | GL - 1 |

| ABBR   | EVIATION                                                          | AB - 1 |

## **FIGURES**

| <b>F</b> ' 11 | pag                                                                  |   |

|---------------|----------------------------------------------------------------------|---|

| Figure 1.1    | Example of SCSI configuration                                        |   |

| Figure 1.2    | Interface signals1-3                                                 |   |

| Figure 1.3    | DATA BUS and SCSI ID1-4                                              |   |

| Figure 1.4    | SCSI interface connector (IDD side) (16-bit SCSI)1-8                 |   |

| Figure 1.5    | SCSI interface connector (cable side) (16-bit SCSI)                  |   |

| Figure 1.6    | Single-ended connector pin assignment (16-bit SCSI)1-10              |   |

| Figure 1.7    | Low-Voltage-Differential connector pin assignment (16-bit SCSI)1-11  |   |

| Figure 1.8    | SCA-2 type, 16-bit SCSI interface connector (IDD side)1-12           |   |

| Figure 1.9    | SCA-2 Type, single-ended 16-bit SCSI connector signal assignment1-13 |   |

| Figure 1.10   | SCA Type, Low-Voltage-Differential connector signal assignment1-14   |   |

| Figure 1.11   | Connection of interface cable1-16                                    |   |

| Figure 1.12   | Single-Ended SCSI termination circuit-11-17                          |   |

| Figure 1.13   | Single-Ended SCSI termination circuit-21-18                          |   |

| Figure 1.14   | LVD SCSI termination circuit                                         |   |

| Figure 1.15   | Circuit for mated indications1-23                                    |   |

| Figure 1.16   | 16-bit SCSI (not SCA2) terminating resistor circuit                  |   |

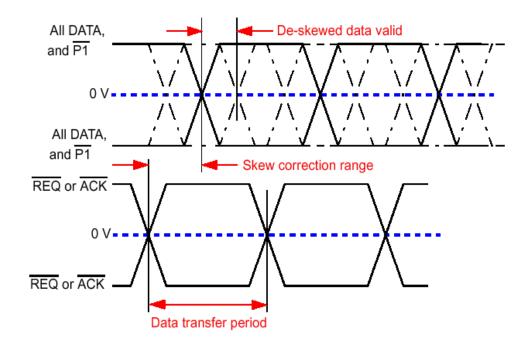

| Figure 1.17   | Receiver de-skew parameters1-38                                      |   |

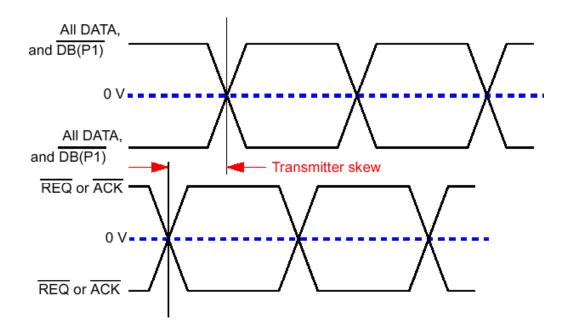

| Figure 1.18   | Transmitter skew1-40                                                 |   |

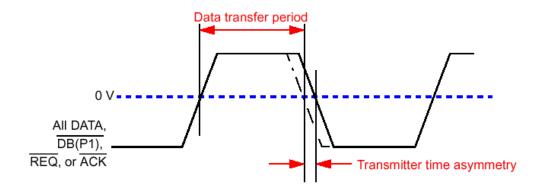

| Figure 1.19   | Transmitter time asymmetry1-41                                       |   |

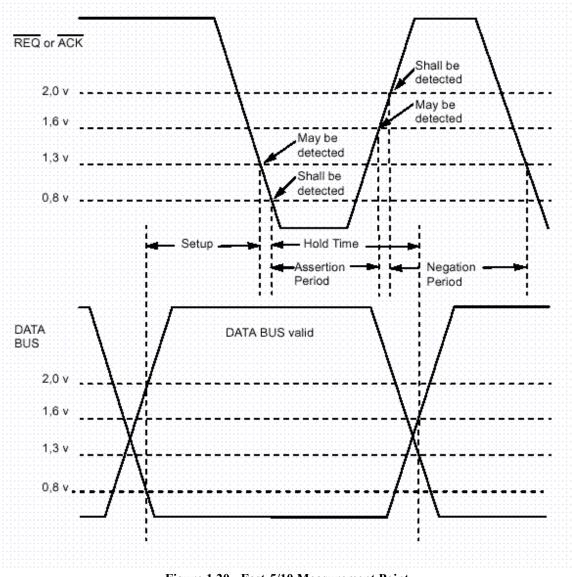

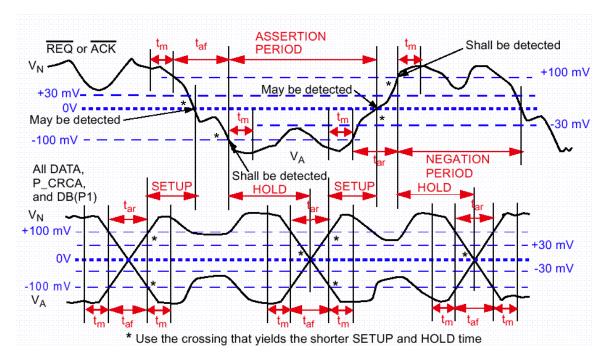

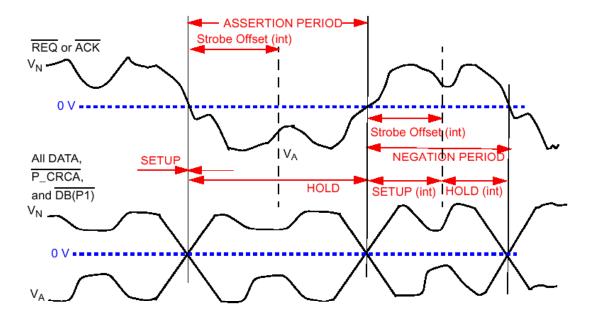

| Figure 1.20   | Fast-5/10 Measurement Point1-42                                      |   |

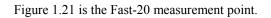

| Figure 1.21   | Fast-20 Measurement Point1-43                                        |   |

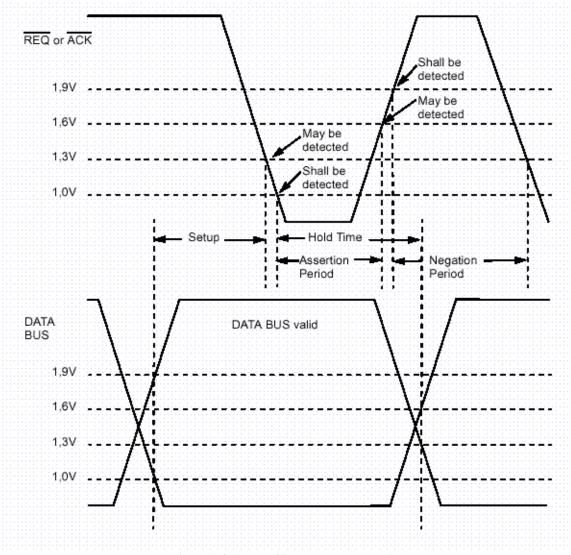

| Figure 1.22   | LVD ST Data Transfer measurement point1-44                           |   |

| Figure 1.23   | LVD DT Data Transfer measurement point1-45                           |   |

| Figure 1.24   | LVD mode DT paced transfer easurement point1-46                      |   |

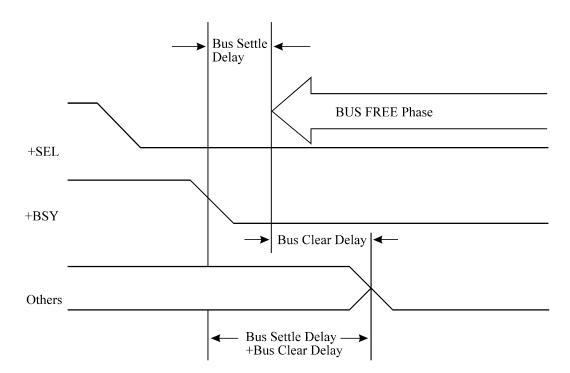

| Figure 1.25   | BUS FREE phase1-48                                                   |   |

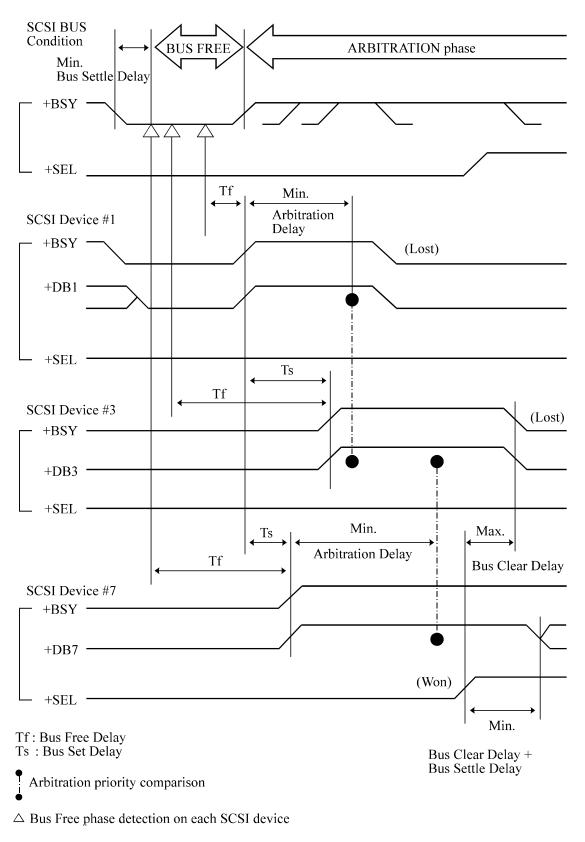

| Figure 1.26   | ARBITRATION phase1-51                                                |   |

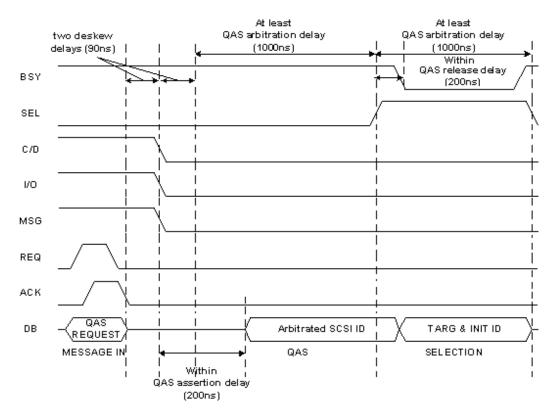

| Figure 1.27   | QAS phase1-54                                                        |   |

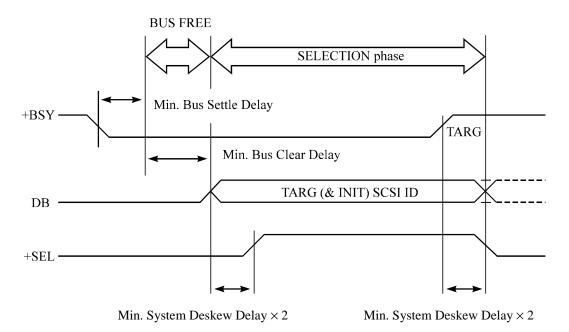

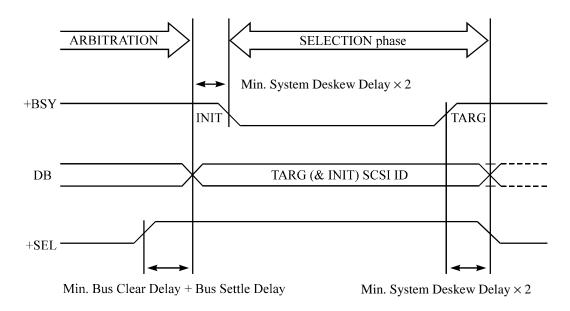

| Figure 1.28   | SELECTION phase1-57                                                  |   |

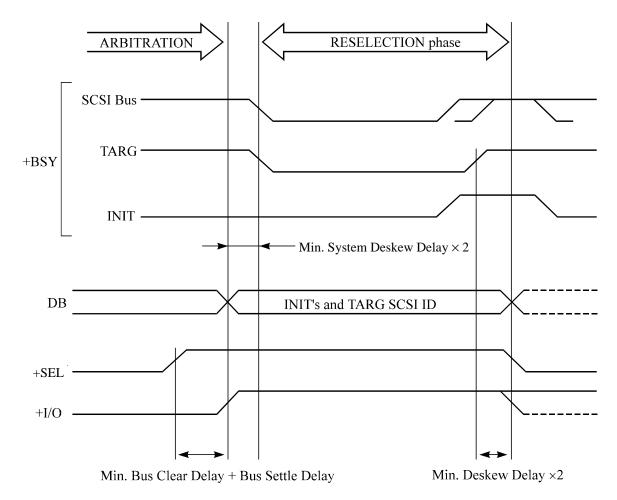

| Figure 1.29   | RESELECTION phase1-60                                                | 1 |

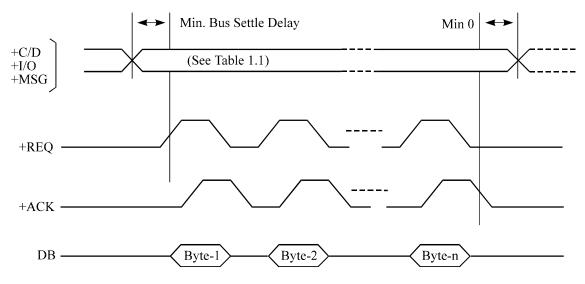

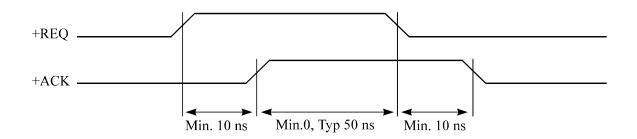

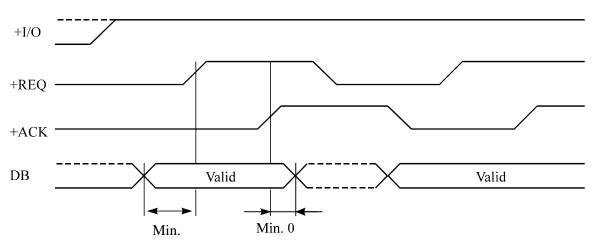

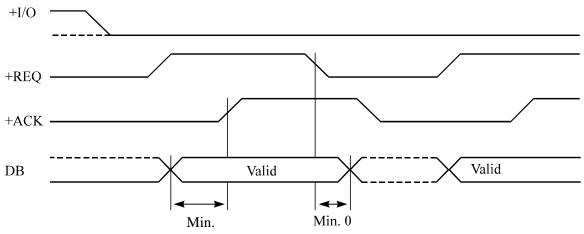

| Figure 1.30   | INFORMATION TRANSFER phase (phase control)1-61                       |   |

| Figure 1.31   | Transfer in asynchronous mode1-64                                    |   |

| Figure 1.32   | ST transfer in synchronous mode1-68                                  |   |

| Figure 1.33   | Data Group Pad field and pCRC field transfer1-74                     |   |

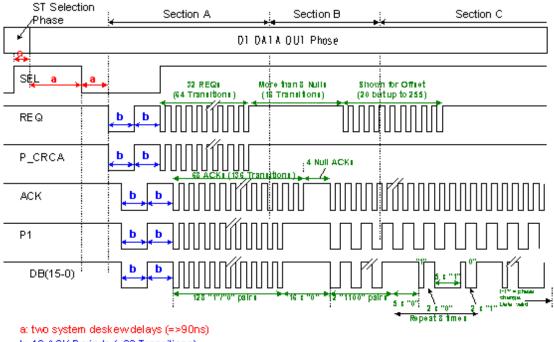

| Figure 1.34 | DT DATA IN phase training pattern                                                                                                  | 1-78  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 1.35 | DT DATA OUT phase training pattern                                                                                                 | 1-80  |

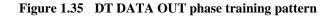

| Figure 1.36 | Usage of P1 to establish data valid and data invalid states                                                                        | 1-81  |

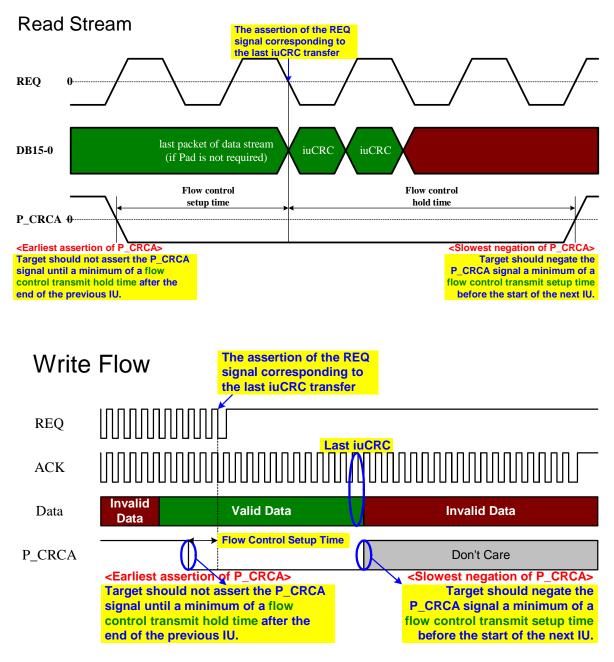

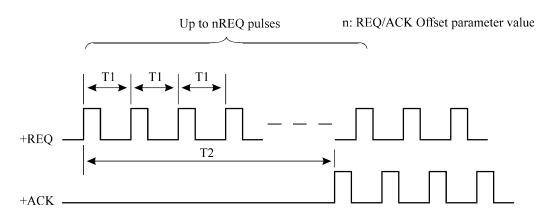

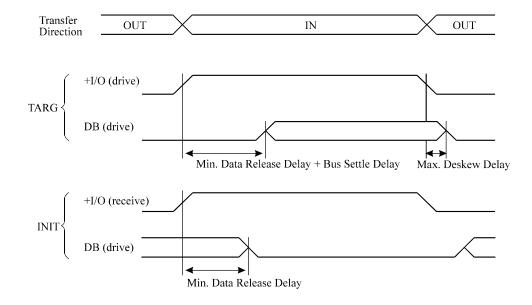

| Figure 1.37 | READ STREAM and WRITE FLOW                                                                                                         | 1-84  |

| Figure 1.38 | Data sequence at data transfer                                                                                                     | 1-87  |

| Figure 1.39 | Data transfer rate in synchronous mode                                                                                             | 1-89  |

| Figure 1.40 | Switching direction of transfer over data bus                                                                                      | 1-91  |

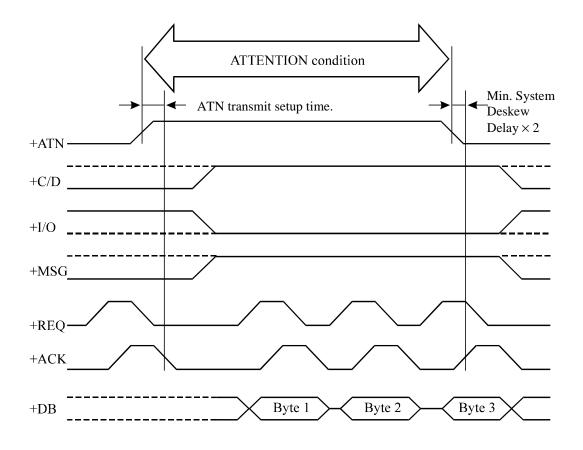

| Figure 1.41 | ATTENTION condition                                                                                                                | 1-95  |

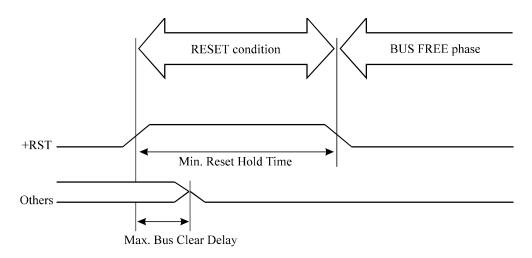

| Figure 1.42 | condition                                                                                                                          | 1-97  |

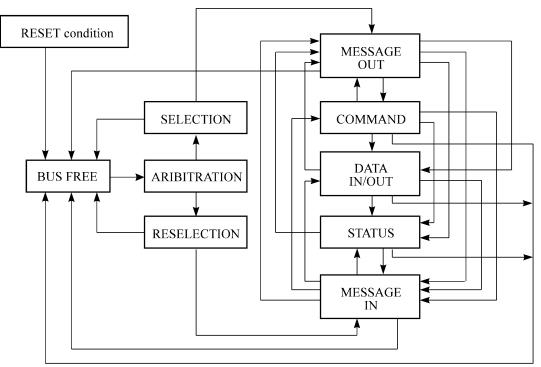

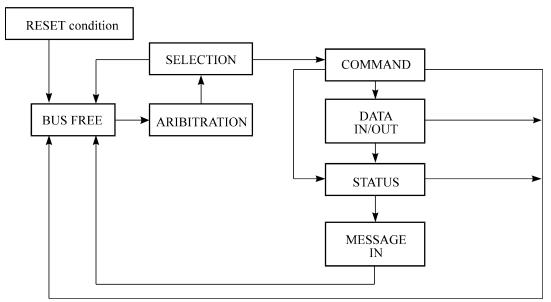

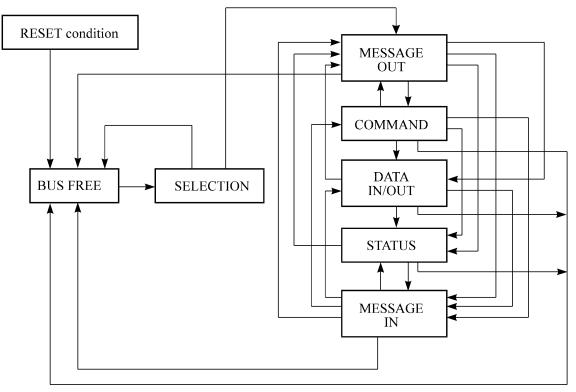

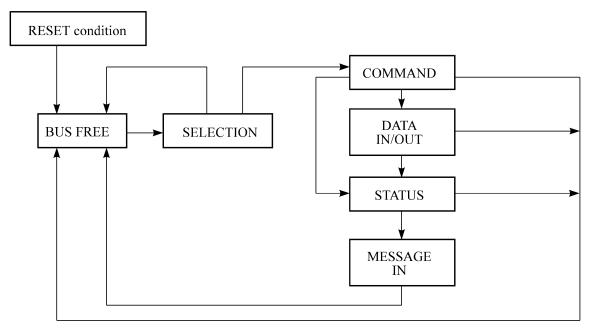

| Figure 1.43 | Bus phase sequence                                                                                                                 | 1-98  |

| Figure 1.44 | Example of bus phase transition at execution of a single command                                                                   | 1-100 |

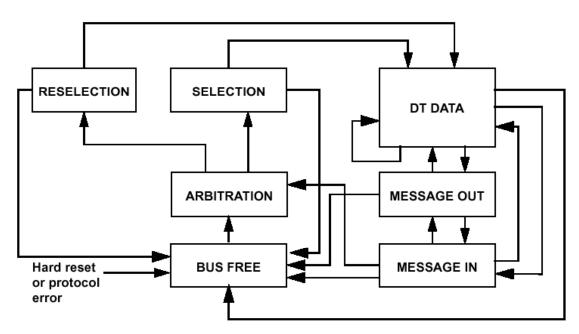

| Figure 1.45 | Phase sequences for physical reconnection or selection without<br>using attentioncondition with information unit transfers enabled | 1-105 |

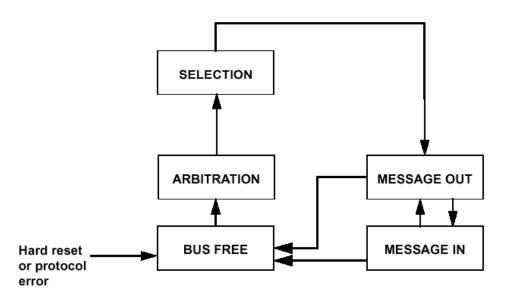

| Figure 1.46 | Phase sequences for selection with attention condition<br>with information unit transfers enabled                                  | 1-106 |

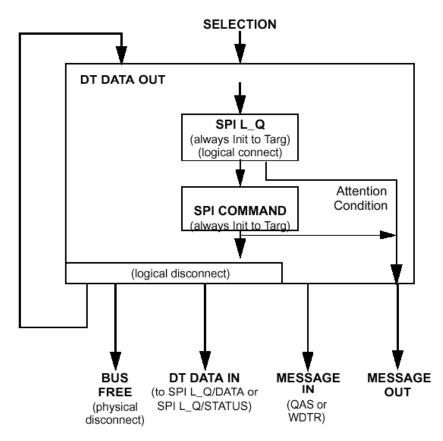

| Figure 1.47 | SPI information unit sequence during initial connection                                                                            | 1-109 |

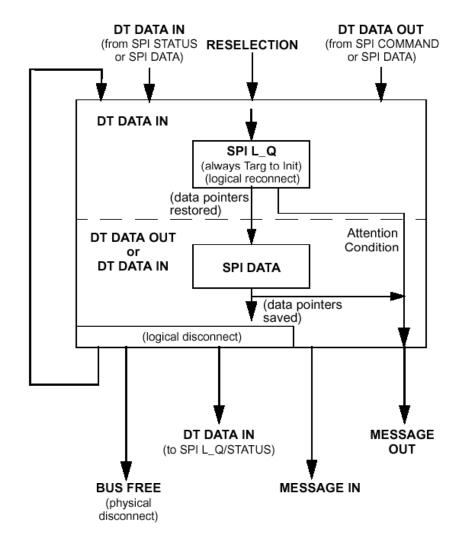

| Figure 1.48 | SPI information unit sequence during data type transfers                                                                           | 1-110 |

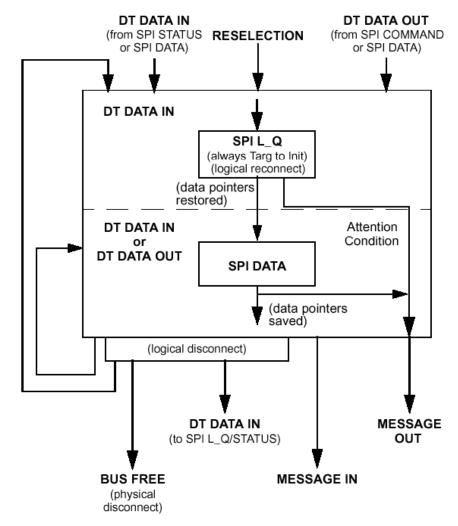

| Figure 1.49 | SPI information unit sequence during data stream type transfers                                                                    | 1-111 |

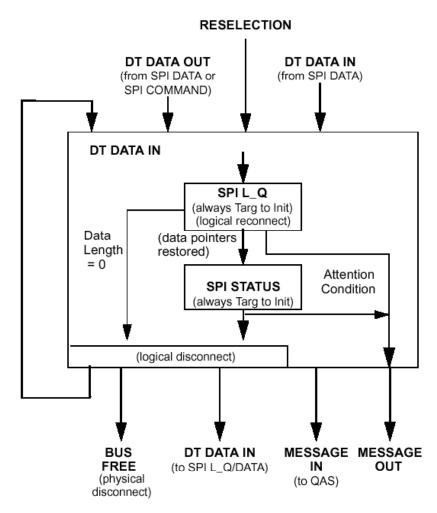

| Figure 1.50 | SPI information unit sequence during status transfers                                                                              | 1-112 |

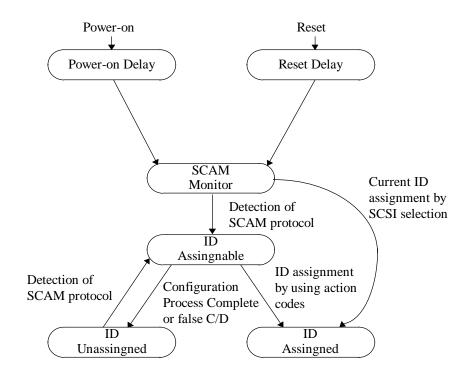

| Figure 1.51 | State of level-1 SCAM target                                                                                                       | 1-126 |

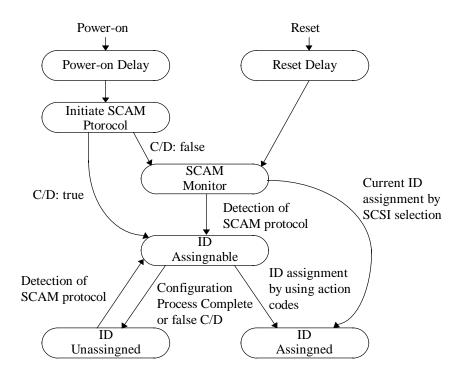

| Figure 1.52 | State of level-2 SCAM target                                                                                                       | 1-127 |

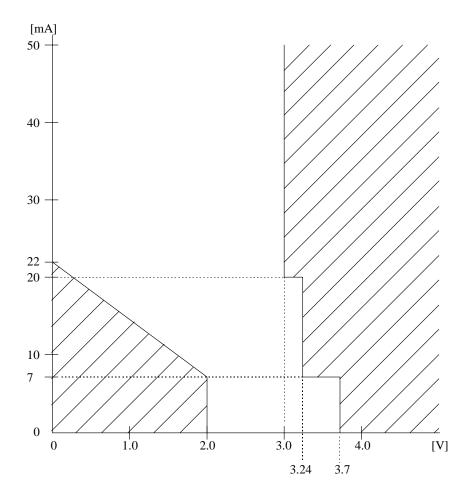

| Figure 1.53 | Comparison of active negate current and voltage                                                                                    | 1-132 |

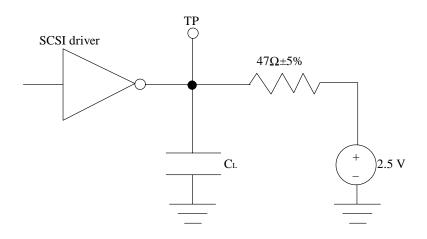

| Figure 1.54 | Single-ended test circuit                                                                                                          | 1-133 |

| Figure 1.55 | LVD transceiver architecture                                                                                                       | 1-135 |

| Figure 1.56 | Connection to the LVD receivers                                                                                                    | 1-136 |

| Figure 1.57 | Differential SCSI bus capacitive loading                                                                                           | 1-137 |

| Figure 2.1  | Message format                                                                                                                     | 2-2   |

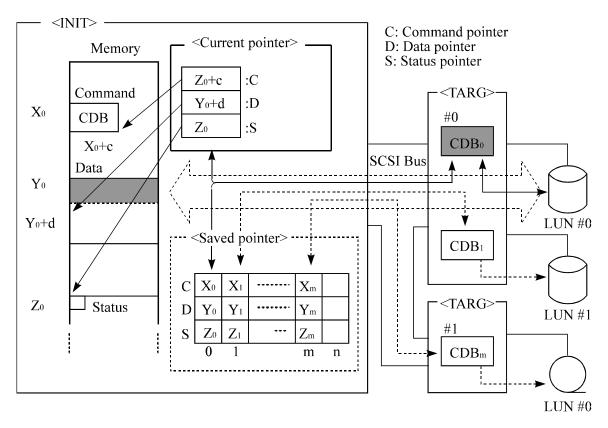

| Figure 2.2  | SCSI pointer configuration                                                                                                         | 2-7   |

## **TABLES**

|            |                                                                                         | page  |

|------------|-----------------------------------------------------------------------------------------|-------|

| Table 1.1  | INFORMATION TRANSFER phase identification                                               | 1-6   |

| Table 1.2  | Single-Ended maximum distance between terminators                                       | 1-7   |

| Table 1.3  | LVD maximum distance between terminators                                                | 1-8   |

| Table 1.4  | SE and LVD Transmission line impedance of cable at maximum indicated data transfer rate | 1-15  |

| Table 1.5  | Attenuation Requiaments for SCSI cable media                                            | 1-15  |

| Table 1.6  | Output characteristic                                                                   | 1-19  |

| Table 1.7  | Input characteristic                                                                    | 1-19  |

| Table 1.8  | LVD DIFFSENS driver specifications                                                      | 1-21  |

| Table 1.9  | DIFFSENS receiver operating requirements                                                | 1-21  |

| Table 1.10 | Requirements for terminating resistor power supply                                      | 1-23  |

| Table 1.11 | Setting set up pin, 16-bit (wide)/8-bit (narrow) mode                                   | 1-25  |

| Table 1.12 | Signal status at receiving end                                                          | 1-26  |

| Table 1.13 | Signal driving method                                                                   | 1-26  |

| Table 1.14 | Bus phases and signal sources                                                           | 1-27  |

| Table 1.15 | SCSI bus control timing values                                                          | 1-28  |

| Table 1.16 | SCSI bus data & information phase ST timing values                                      | 1-29  |

| Table 1.17 | Miscellaneous SCSI bus data & information phase DT timing values                        | 1-29  |

| Table 1.18 | SCSI bus data & information phase DT timing values                                      | 1-30  |

| Table 1.19 | Receive SCSI bus data & information phase DT timing values                              | 1-31  |

| Table 1.20 | Parameters used for fast synchronous data transfer mode                                 | 1-88  |

| Table 1.21 | Retry count setting for RESELECTION phase                                               | 1-92  |

| Table 1.22 | SPI command information unit                                                            | 1-114 |

| Table 1.23 | TASK ATTRIBUTE                                                                          | 1-114 |

| Table 1.24 | TASK MANAGEMENT FUNCTIONS                                                               | 1-115 |

| Table 1.25 | SPI L_Q information unit                                                                | 1-116 |

| Table 1.26 | TYPE                                                                                    | 1-117 |

| Table 1.27 | BIDI DIRECTION                                                                          | 1-118 |

| Table 1.28 | SPI data information unit                                                               | 1-119 |

| Table 1.29 | SPI data stream information unit                                                        | 1-120 |

| Table 1.30 | SPI status information unit                                                             | 1-121 |

| Table 1.31 | PACKETIZED FAILURES field                                                               | 1-122 |

| Table 1.32 | PACKETIZED FAILURE CODE                                                                 | 1-123 |

| Table 1.33 | Maximum capacitance                                  | 1-138 |

|------------|------------------------------------------------------|-------|

| Table 1.34 | System level requirements                            | 1-139 |

| Table 2.1  | SCSI message                                         | 2-3   |

| Table 2.2  | Extended message                                     | 2-4   |

| Table 2.3  | Definition of data transfer mode by message exchange | 2-17  |

| Table 2.4  | Synchronous mode data transfer request setting       | 2-19  |

| Table 2.5  | Transfer mode setup request from INIT to IDD         | 2-21  |

| Table 2.6  | Transfer mode setup request from IDD to INIT         | 2-23  |

| Table 2.7  | Data bus width defined by message exchange           | 2-25  |

| Table 2.8  | Wide mode setting request from the INIT to the IDD   | 2-27  |

| Table 2.9  | Wide mode setting request from the IDD to the INIT   | 2-28  |

| Table 2.10 | TRANSFER PERIOD FACTOR field                         | 2-29  |

| Table 2.11 | Valid protocol options bit combinations              | 2-31  |

| Table 2.12 | PARALLEL PROTOCOL REQUEST message implied agreement  | 2-33  |

| Table 3.1  | Retry procedure for SCSI error                       | 3-7   |

This page is intentionally left blank.

## CHAPTER 1 SCSI BUS

| 1.1  | System Configuration        |

|------|-----------------------------|

| 1.2  | Interface Signal Definition |

| 1.3  | Physical Requirements       |

| 1.4  | Electrical Requirements     |

| 1.5  | Timing Rule                 |

| 1.6  | Bus Phases                  |

| 1.7  | Bus Conditions              |

| 1.8  | Bus Phase Sequence          |

| 1.9  | SPI information units       |

| 1.10 | SCAM                        |

| 1.11 | Ultra SCSI                  |

| 1.12 | Low-Voltage Differential    |

| 1.13 | SCSI Bus Fairness           |

This chapter describes the configuration, physical and electrical characteristics, interface protocol, and operations of SCSI buses.

#### Note:

The IDD operates as a target (TARG) on the SCSI bus. The IDD is called "TARG" in this chapter except when clear identification is required.

#### 1.1 System Configuration

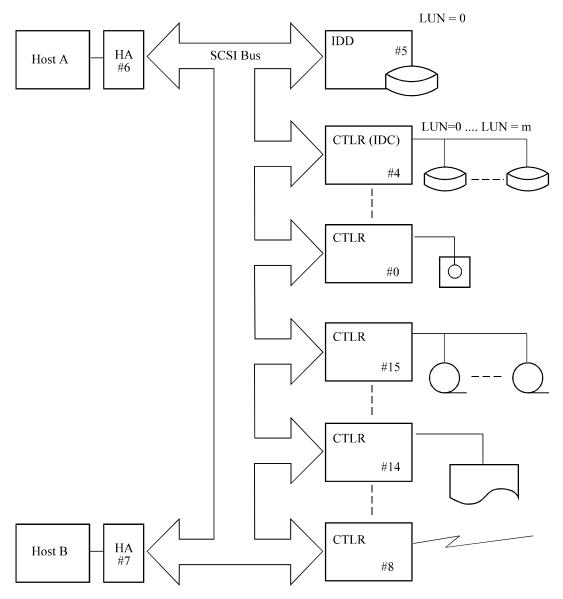

Up to 16-bit SCSI series models can be connected to the system via the SCSI bus. Figure 1.1 gives an example of multi-host system configuration.

Each SCSI device operates as an initiator (INIT) or a target (TARG). Only a single INIT and a single TARG selected by this INIT can operate simultaneously on the SCSI bus.

The system configuration allows any combination of a SCSI device to operate as the INIT and a SCSI device to operate as the TARG. Also, any device having both the INIT and TARG functions can be used on the SCSI bus.

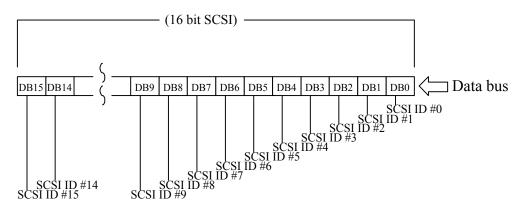

Each SCSI device is assigned a unique address (or SCSI ID). The SCSI ID corresponds to a bit number of the SCSI data bus. While the INIT uses a logical unit number (LUN) to select an I/O unit to be connected under TARG control.

Any SCSI ID of the IDD can be selected using the setup pins. However, the LUN is fixed to zero (0). The SCSI ID can be 0 to 15.

#### Note:

The maximum number of SCSI devices and the maximum cable length are limited depending on the selected SCSI data transfer mode and the SCSI transceiver type. Appropriate SCSI devices and cable length must be determined for each system.

#n : SCSI ID, HA: Host adapter

Figure 1.1 Example of SCSI configuration

#### **1.2** Interface Signal Definition

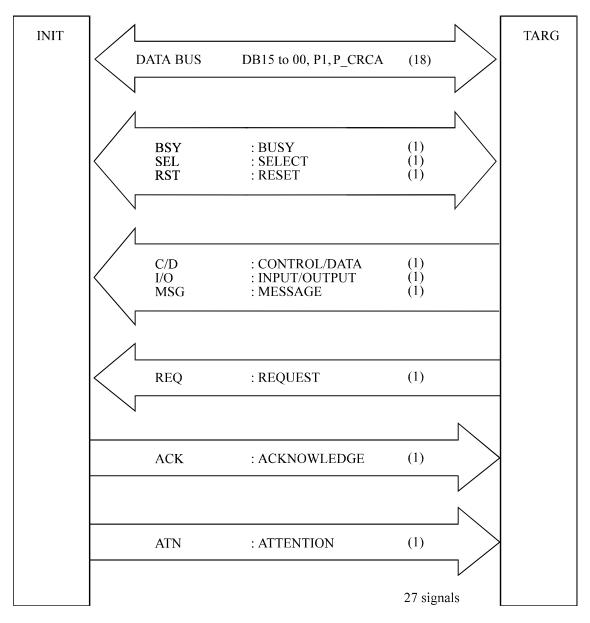

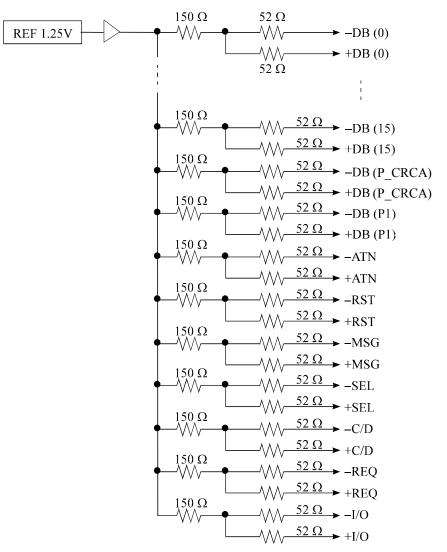

Figure 1.2 shows interface signal types. The SCSI bus consists of 27 signal lines. The 27 signal lines consist of data buses (2 bytes plus two odd parity bits) and 9 control signal lines.

The SCSI bus can be a single-ended or low voltage differential(LVD) interface depending on the model used. Their physical and electrical characteristics are detailed in Sections 1.3 and 1.4.

Figure 1.2 Interface signals

(1) DB15 to DB00, P1, P\_CRCA (Data buses)

The 16-bit SCSI system uses a bidirectional data bus consisting of two-byte data and two odd parity bits.

MSB (2<sup>15</sup>): DB15, LSB (2<sup>0</sup>): DB00

The data bus is used to transfer a command, data, a status, or a message in the INFORMATION TRANSFER phase. However, DB15 to DB08 and P1 are used for data transfer only. The data is transferred only after the WIDE DATA TRANSFER REQUEST or PARALLEL PROTOCOL REQUEST message has been exchanged and the 16-bit data transfer mode has been established between the INIT and TARG.

In the ARBITRATION phase, the data bus is used to send a SCSI ID to determine the bus arbitration priority. In the SELECTION or RESELECTION phase, the data bus is used to send a SCSI ID of the INIT and TARG. Figure 1.3 shows the relationship between the data buses and SCSI IDs.

Figure 1.3 DATA BUS and SCSI ID

#### (a) DB15 to 0

Sixteen data-bit signals that form the 16-bit DATA BUS.

(b) DB7 to 0

Eight data-bit signals that form the 16-bit DATA BUS.

(c) P1 (ST DATA phase)

A signal sourced by the SCSI device driving the data bus during ST DATA phases. This signal is associated with the DB(15-8) signals and is used to detect the presence of an odd number of bit errors within the byte. The parity bit is driven such that the number of logical ones in the byte plus the parity bit is odd.

(d) P1 (data group transfer enabled)

A signal that shall be continuously negated by the SCSI device driving the DB(15-0) signals and shall be ignored by the SCSI device receiving the DB(15-0) signals during DT DATA phases.

(e) P1 (information unit and paced transfer enabled)

A signal that is sourced by SCSI device to indicate the data valid or data invalid state.

(f) P\_CRCA (PARITY/CRC AVAILABLE) (SELECTION phase, ST DATA phase, COMMAND phase, MESSAGE phase, or STATUS phase)

A signal sourced by the SCSI device driving the data bus during these phases. This signal is associated with the DB(7-0) signals and is used to detect the presence of an odd number of bit errors within the byte. The parity bit is driven such that the number of logical ones in the byte plus the parity bit is odd.

The parity bits (P1 and P\_CRCA) is optional for the system. The IDD handles the data bus parity as follows:

- The IDD has the data bus parity check function, and can enable or disable the parity check. See Section 5.3.2 "SCSI Parity" of the Product Manual for setup details.

- When valid data is sent to the data bus from the IDD, the parity data is always guaranteed except for the ARBITRATION phase.

- (g) P\_CRCA (data group transfer enabled)

A signal sourced by a target during DT DATA phases to control whether a data group field is a pad field, pCRC field, or data field. When asserted the data group field shall be pad or pCRC fields that shall not be transferred to the ULP. When negated the data group field shall be a data field that shall be transferred to the ULP.

#### Note:

ULP is "Upper Level Protocol".

(h) P\_CRCA (information unit and paced transfer enabled)

During DT DATA phases when information unit transfers are enabled this signal is referred to as P\_CRCA and is sourced by the SCSI target port. Depending on the negotiated condition of read streaming and write flow control the SCSI initiator port and SCSI target port usage for P\_CRCA is different. When information unit transfers are enabled the SCSI target port and SCSI initiator port shall use the P\_CRCA signal.

#### (2) BSY (BUSY)

The BSY signal indicates that the SCSI bus is in use. In the ARBITRATION phase, this signal is used to request for the bus usage priority.

#### (3) SEL (SELECT)

The SEL signal is used by the INIT to select a TARG (in the SELECTION phase) or by the TARG to reselect an INIT (in the RESELECTION phase).

#### (4) C/D (CONTROL/DATA)

This is a combination of I/O and MSG signals, and specifies a type of information transferred on the data bus. The C/D signal is always driven by the TARG (see Table 1.1).

#### (5) I/O (INPUT/OUTPUT)

The I/O signal specifies the information transmission direction on the data bus. It is also used to identify the SELECTION phase or RESELECTION phase. This signal is always driven by the TARG (see Table 1.1).

#### (6) MSG (MESSAGE)

A signal sourced by a target to indicate the MESSAGE phase or a DT DATA phase depending on whether C/D is true or false. Asserted indicates MESSAGE or DT DATA (see Table 1.1).

| Signal |     |     | Phase       | Direction    | Direction Comment |            |

|--------|-----|-----|-------------|--------------|-------------------|------------|

| C/D    | MSG | I/O | rllase      | Direction    | Com               | inent      |

| 0      | 0   | 0   | ST DATA OUT | INIT -> TARG | ST Data phase     |            |

| 0      | 0   | 1   | ST DATA IN  | INIT <- TARG | ST Data phase     | Data phasa |

| 0      | 1   | 0   | DT DATA OUT | INIT -> TARG | DT Data phaga     | Data phase |

| 0      | 1   | 1   | DT DATA IN  | INIT <- TARG | DT Data phase     |            |

| 1      | 0   | 0   | COMMAND     | INIT -> TARG |                   |            |

| 1      | 0   | 1   | STATUS      | INIT <- TARG |                   |            |

| 1      | 1   | 0   | MESSAGE OUT | INIT -> TARG | MESSAGE           |            |

| 1      | 1   | 1   | MESSAGE IN  | INIT <- TARG | MESSAGE           |            |

#### Table 1.1 INFORMATION TRANSFER phase identification

#### (7) REQ (REQUEST)

This is a transmission request from the TARG to the INIT in the INFORMATION TRANSFER phase.

#### (8) ACK (ACKNOWLEDGE)

The ACK signal is a response to the REQ signal sent from the INIT to TARG in the INFORMATION TRANSFER phase.

#### (9) ATN (ATTENTION)

The ATN signal indicates that the INIT has a message to be sent to the TARG. It is used to generate an ATTENTION condition.

#### (10) RST (RESET)

The RST signal is a Reset signal to clear all SCSI devices on the bus (to the RESET condition).

#### 1.3 Physical Requirements

All SCSI devices are connected to each other in a daisy chain. Both ends of the interface cable are terminated with resistor.

Tables 1.2 and 1.3 define the SCSI bus electrical characteristics (for interface signal driver/receiver).

| Number of        | Maximum distance between terminators (meters) |         |         |  |

|------------------|-----------------------------------------------|---------|---------|--|

| attached devices | FAST-5                                        | FAST-10 | FAST-20 |  |

| 2 to 4 devices   | 6                                             | 3       | 3       |  |

| 5 to 8 devices   | 6                                             | 3       | 1.5     |  |

| 9 to 16 devices  | 6                                             | 3       | N/A     |  |

#### Table 1.2 Single-Ended maximum distance between terminators

| Interconnect   | Maximum distance between terminators (meters) |         |         |         |         |          |

|----------------|-----------------------------------------------|---------|---------|---------|---------|----------|

| Interconnect   | Fast-5                                        | Fast-10 | Fast-20 | Fast-40 | Fast-80 | Fast-160 |

| Point-to-point | 25                                            | 25      | 25      | 25      | 25      | 25       |

| Multidrop      | 12                                            | 12      | 12      | 12      | 12      | 12       |

#### Table 1.3 LVD maximum distance between terminators

#### **1.3.1** Interface connector

#### (1) Interface connector of the 16-bit SCSI

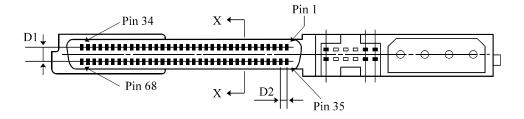

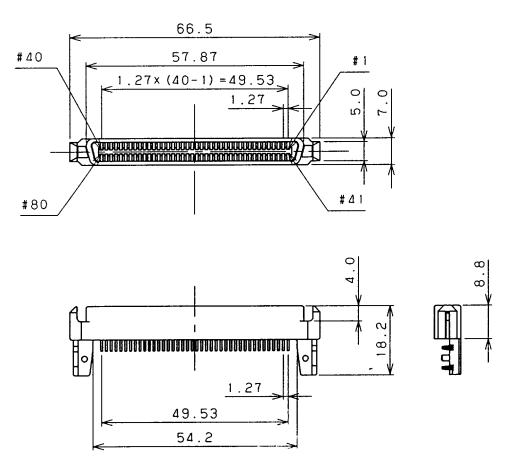

The IDD 16-bit SCSI bus connector is nonshielded 68-pin, consisting of two 34-pin rows with adjacent pins 1.27 mm (0.05 inch) part (Figure 1.4).

For the interface cable connector, use a nonshielded 68-contact socket consisting of two 34-contact rows points with adjacent contact points 1.27 mm (0.05 inch) apart (Figure 1.5).

Figure 1.6 shows single-ended interface connector signal assignment.

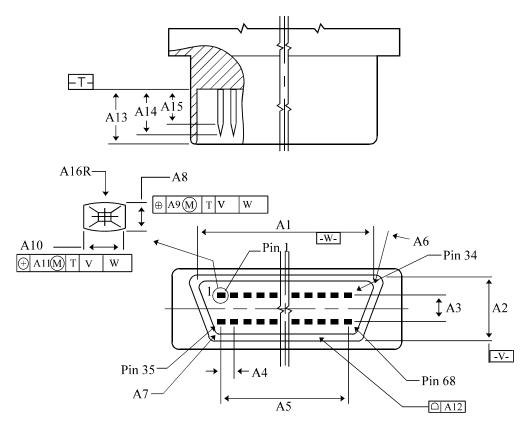

Figure 1.7 shows low-voltage-differential interface connector signal assignment.

| Symbol | mm   | inch  | Remarks |

|--------|------|-------|---------|

| D1     | 2.54 | 0.100 |         |

| D2     | 1.27 | 0.050 |         |

Note:

The tolerance is  $\pm 0.127$  mm (0.005 inch) unless otherwise specified.

#### Figure 1.4 SCSI interface connector (IDD side) (16-bit SCSI)

| Dimensions | 68 pos       | sition              |

|------------|--------------|---------------------|

| Dimensions | Millimeters  | Inches              |

| Al         | 46.28        | 1.822               |

| A2         | 5.69         | 0.224               |

| A3         | 2.54         | 0.100               |

| A4         | 1.27         | 0.050               |

| A5         | 41.91        | 1.650               |

| A6         | 15°          | 15°                 |

| A7         | 1.04R        | 0.041R              |

| A8         | 0.396 ±0.010 | 0.0156±0.0004       |

| A9         | 0.23         | 0.009               |

| A10        | 0.61±0.03    | $0.024 {\pm} 0.001$ |

| A11        | 0.23         | 0.009               |

| A12        | 0.05         | 0.002               |

| A13        | 5.16 ±0.15   | 0.203±0.006         |

| A14        | 4.39 Max.    | 0.173 Max.          |

| A15        | 3.02 Min.    | 0.119 Min.          |

| A16        | 1.02±0.25    | 0.040±0.010         |

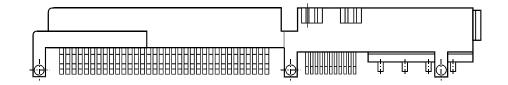

Figure 1.5 SCSI interface connector (cable side) (16-bit SCSI)

| Pin No. | Signal     | Signal     | Pin No. |

|---------|------------|------------|---------|

| 01      | GND        | -DB12      | 35      |

| 02      | GND        | -DB13      | 36      |

| 03      | GND        | -DB14      | 37      |

| 04      | GND        | -DB15      | 38      |

| 05      | GND        | -DBP1      | 39      |

| 06      | GND        | -DB00      | 40      |

| 07      | GND        | -DB01      | 41      |

| 08      | GND        | -DB02      | 42      |

| 09      | GND        | -DB03      | 43      |

| 10      | GND        | -DB04      | 44      |

| 11      | GND        | -DB05      | 45      |

| 12      | GND        | -DB06      | 46      |

| 13      | GND        | -DBP7      | 47      |

| 14      | GND        | -P_CRCA    | 48      |

| 15      | GND        | GND        | 49      |

| 16      | GND        | GND        | 50      |

| 17      | TERMPWR *  | TERMPWR *  | 51      |

| 18      | TERMPWR *  | TERMPWR *  | 52      |

| 19      | (reserved) | (reserved) | 53      |

| 20      | GND        | GND        | 54      |

| 21      | GND        | -ATN       | 55      |

| 22      | GND        | GND        | 56      |

| 23      | GND        | -BSY       | 57      |

| 24      | GND        | -ACK       | 58      |

| 25      | GND        | -RST       | 59      |

| 26      | GND        | -MSG       | 60      |

| 27      | GND        | -SEL       | 61      |

| 28      | GND        | -C/D       | 62      |

| 29      | GND        | -REQ       | 63      |

| 30      | GND        | -I/O       | 64      |

| 31      | GND        | -DB08      | 65      |

| 32      | GND        | -DB09      | 66      |

| 33      | GND        | -DB10      | 67      |

| 34      | GND        | -DB11      | 68      |

\* Terminating resistor power

Figure 1.6 Single-ended connector pin assignment (16-bit SCSI)

| Pin No. | Signal    | Signal    | Pin No. |

|---------|-----------|-----------|---------|

| 01      | +DB(12)   | -DB(12)   | 35      |

| 02      | +DB(13)   | -DB(13)   | 36      |

| 03      | +DB(14)   | -DB(14)   | 37      |

| 04      | +DB(15)   | -DB(15)   | 38      |

| 05      | +DB(P1)   | -DB(P1)   | 39      |

| 06      | +DB(0)    | -DB(0)    | 40      |

| 07      | +DB(1)    | -DB(1)    | 41      |

| 08      | +DB(2)    | -DB(2)    | 42      |

| 09      | +DB(3)    | -DB(3)    | 43      |

| 10      | +DB(4)    | -DB(4)    | 44      |

| 11      | +DB(5)    | -DB(5)    | 45      |

| 12      | +DB(6)    | -DB(6)    | 46      |

| 13      | +DB(7)    | -DB(7)    | 47      |

| 14      | +P_CRCA   | -P_CRCA   | 48      |

| 15      | GROUND    | GROUND    | 49      |

| 16      | DIFFSENS  | GROUND    | 50      |

| 17      | TERMPWR * | TERMPWR * | 51      |

| 18      | TERMPWR * | TERMPWR * | 52      |

| 19      | RESERVED  | RESERVED  | 53      |

| 20      | GROUND    | GROUND    | 54      |

| 21      | +ATN      | -ATN      | 55      |

| 22      | GROUND    | GROUND    | 56      |

| 23      | +BSY      | -BSY      | 57      |

| 24      | +ACK      | -ACK      | 58      |

| 25      | +RST      | -RST      | 59      |

| 26      | +MSG      | -MSG      | 60      |

| 27      | +SEL      | -SEL      | 61      |

| 28      | +C/D      | -C/D      | 62      |

| 29      | +REQ      | -REQ      | 63      |

| 30      | +I/O      | -I/O      | 64      |

| 31      | +DB(8)    | -DB(8)    | 65      |

| 32      | +DB(9)    | -DB(9)    | 66      |

| 33      | +DB(10)   | -DB(10)   | 67      |

| 34      | +DB(11)   | -DB(11)   | 68      |

\* Terminating resistor power

#### (2) Interface connector of SCA-2 type 16-bit SCSI

The 16-bit, SCA-2 type SCSI bus connectors of the IDD are 80-pin, unshielded connectors, each having two rows of 40 parallel pins (separated 1.27 mm or 0.05" from each other) (see Figure 1.8).

Figure 1.9 shows the pin assignment of 16-bit, SCA-2 type single-ended SCSI interface connector.

Figure 1.8 SCA-2 type, 16-bit SCSI interface connector (IDD side)

| Pin No. | Signal          | Signal             | Pin No. |

|---------|-----------------|--------------------|---------|

| 01      | +12V (CHARGE)   | 12V RETURN (GND)   | 41      |

| 02      | +12V            | 12V RETURN (GND)   | 42      |

| 03      | +12V            | 12V RETURN (GND)   | 43      |

| 04      | +12V            | MATED1             | 44      |

| 05      | reserved (N.C.) | reserved (N.C.)    | 45      |

| 06      | reserved (N.C.) | GND                | 46      |

| 07      | -DB11           | GND                | 47      |

| 08      | -DB10           | GND                | 48      |

| 09      | -DB09           | GND                | 49      |

| 10      | -DB08           | GND                | 50      |

| 11      | -I/O            | GND                | 51      |

| 12      | -REQ            | GND                | 52      |

| 13      | -C/D            | GND                | 53      |

| 14      | -SEL            | GND                | 54      |

| 15      | -MSG            | GND                | 55      |

| 16      | -RST            | GND                | 56      |

| 17      | -ACK            | GND                | 57      |

| 18      | -BSY            | GND                | 58      |

| 19      | -ATN            | GND                | 59      |

| 20      | -P_CRCA         | GND                | 60      |

| 21      | -DB07           | GND                | 61      |

| 22      | -DB06           | GND                | 62      |

| 23      | -DB05           | GND                | 63      |

| 24      | -DB04           | GND                | 64      |

| 25      | -DB03           | GND                | 65      |

| 26      | -DB02           | GND                | 66      |

| 27      | -DB01           | GND                | 67      |

| 28      | -DB00           | GND                | 68      |

| 29      | -DBP1           | GND                | 69      |

| 30      | -DB15           | GND                | 70      |

| 31      | -DB14           | GND                | 71      |

| 32      | -DB13           | GND                | 72      |

| 33      | -DB12           | GND                | 73      |

| 34      | 5V              | 5V RETURN (MATED2) | 74      |

| 35      | 5V              | 5V RETURN (GND)    | 75      |

| 36      | 5V (CHARGE)     | 5V RETURN (GND)    | 76      |

| 37      | Reserved        | -LED               | 77      |

| 38      | RMT_START       | DLYD_START         | 78      |

| 39      | SCSI ID0        | SCSI ID1           | 79      |

| 40      | SCSI ID2        | SCSI ID3           | 80      |

Note:

Signal in parentheses indicates for SCA-2 type.

#### Figure 1.9 SCA-2 Type, single-ended 16-bit SCSI connector signal assignment

| Pin No. | Signal         | Signal             | Pin No |

|---------|----------------|--------------------|--------|

| 01      | +12V (CHARGE)  | 12V RETURN (GND)   | 41     |

| 02      | +12V           | 12V RETURN (GND)   | 42     |

| 03      | +12V           | 12V RETURN (GND)   | 43     |

| 04      | +12V           | MATED1             | 44     |

| 05      | reserved(N.C.) | reserved(N.C.)     | 45     |

| 06      | reserved(N.C.) | DIFFSENS           | 46     |

| 07      | -DB(11)        | +DB(11)            | 47     |

| 08      | -DB(10)        | +DB(10)            | 48     |

| 09      | -DB(9)         | +DB(9)             | 49     |

| 10      | -DB(8)         | +DB(8)             | 50     |

| 11      | -I/O           | +I/O               | 51     |

| 12      | -REQ           | +REQ               | 52     |

| 13      | -C/D           | +C/D               | 53     |

| 14      | -SEL           | +SEL               | 54     |

| 15      | -MSG           | +MSG               | 55     |

| 16      | -RST           | +RST               | 56     |

| 17      | -ACK           | +ACK               | 57     |

| 18      | -BSY           | +BSY               | 58     |

| 19      | -ATN           | +ATN               | 59     |

| 20      | -P_CRCA        | +P_CRCA            | 60     |

| 21      | -DB(7)         | +DB(7)             | 61     |

| 22      | -DB(6)         | +DB(6)             | 62     |

| 23      | -DB(5)         | +DB(5)             | 63     |

| 24      | -DB(4)         | +DB(4)             | 64     |

| 25      | -DB(3)         | +DB(3)             | 65     |

| 26      | -DB(2)         | +DB(2)             | 66     |

| 27      | -DB(1)         | +DB(1)             | 67     |

| 28      | -DB(0)         | +DB(0)             | 68     |

| 29      | -DB(P1)        | +DB(P1)            | 69     |

| 30      | -DB(15)        | +DB(15)            | 70     |

| 31      | -DB(14)        | +DB(14)            | 71     |

| 32      | -DB(13)        | +DB(13)            | 72     |

| 33      | -DB(12)        | +DB(12)            | 73     |

| 34      | +5V            | 5V RETURN (MATED2) | 74     |

| 35      | +5V            | 5V RETURN (GND)    | 75     |

| 36      | +5V (CHARGE)   | 5V RETURN (GND)    | 76     |

| 37      | Reserved       | -LED               | 77     |

| 38      | RMT_START      | DLYD_START         | 78     |

| 39      | SCSI ID0       | SCSI ID1           | 79     |

| 40      | SCSI ID2       | SCSI ID3           | 80     |

Figure 1.10 SCA Type, Low-Voltage-Differential connector signal assignment

#### **1.3.2** Interface cable

Use the twisted-pair interface cables satisfying the requirements of Tables 1.4 and 1.5.

## Table 1.4 SE and LVD Transmission line impedance of cable at maximum indicated data transfer rate

| Description | Local SE transmission line<br>impedance |         | Local differential<br>transmission line impedance |          |

|-------------|-----------------------------------------|---------|---------------------------------------------------|----------|

|             | Minimum                                 | Maximum | Minimum                                           | Maximum  |

| All         | 84 Ohms (78<br>Ohms) (Note)             | 96 Ohms | 110 Ohms                                          | 135 Ohms |

Note:

If SCSI loads attached to the cable media are separated by more than 1.0 m use the value of 78 Ohms.

| Table 1.5 | Attenuation Requiaments for SCSI cable media |

|-----------|----------------------------------------------|

|-----------|----------------------------------------------|

| Distance between<br>SCSI bus<br>terminators (meters) | Distances are consistent with these<br>minimum size conductors when used<br>with high quality dielectrics | Notes                  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|

| 0 to 9                                               | $0.0324 \text{ mm}^2$ (32 AWG) solid/<br>$0.05092 \text{ mm}^2$ (30 AWG) stranded                         | multiple loads allowed |

| 0 to 12                                              | 0.05092 mm <sup>2</sup> (30 AWG) solid/<br>0.08042 mm <sup>2</sup> (28 AWG) stranded                      | multiple loads allowed |

| >12 to 25                                            | 0.05092 mm <sup>2</sup> (30 AWG) solid/<br>0.08042 mm <sup>2</sup> (28 AWG) stranded                      | point to point only    |

A twisted-pair cable must consist of pin n and pin n+1 (where "n" is an odd number) of the interface connector. Use the SCSI bus cables having the same impedance characteristics to minimize the signal reflection but keep the highest possible transmission characteristics.

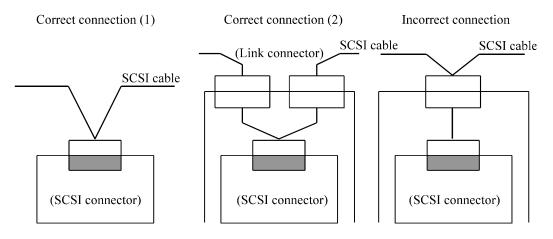

If SCSI devices are connected to the terminals other than the interface cable ends, use the cable branch at the SCSI connectors. No more SCSI cable can be connected to the last SCSI device (which is connected to the SCSI bus) except when it is terminated with the terminator (see Figure 1.11).

The interface cable must have the stub length less than 0.1 meter for the single-ended SCSI cable. Separate the stabs at least 0.3 meter from each other. (Keep the stab at least 30 cm away from a SCSI device.)

#### (a) Connection to a middle point of the cable

(b) Connection to the end of the cable.

Figure 1.11 Connection of interface cable

#### 1.4 Electrical Requirements

#### 1.4.1 Single-Ended type

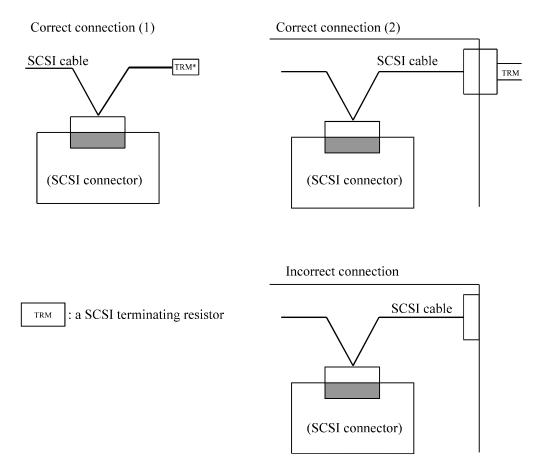

(1) Termination circuit

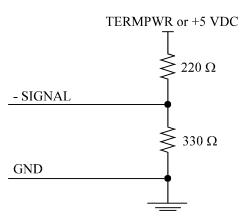

All signals except for RESERVE, GND, or TERMPWR should be terminated at both ends of the bus. Each signal should be terminated by one of the following methods. Figures 1.12 and 1.13 show the termination circuit.

- a) Each signal must connect to the TERMPWR signal through 220  $\Omega$  (within ±5%) resistor, and connect to ground through 330  $\Omega$  (within ±5%) resistor.

- b) The termination circuit of each signal shall satisfy the following conditions.

- 1) The terminators should be powered by the TERMPWR line. The circuit may receive additional power from other sources but not require such additional power for proper operation;

- 2) Each terminator should source current to the signal line whenever its terminal voltage is below 2.5 VDC and this current should not exceed 22.4 mA for any line voltage at or above 0.5 VDC and 25.4 mA for any line voltage between 0.5 VDC and 0.2 VDC even when all other signal lines are driven at 4.0 VDC;

- 3) The voltage on all released signal lines should be at least 2.5 VDC;

- 4) These conditions should be met with any conforming configuration of TARGs and INITs as long as at least one SCSI device is supplying TERMPWR;

- 5) The terminator at each end of the SCSI bus should add a maximum of 25 pF capacitance to each signal;

- 6) The terminator may not source current to the signal line whenever its terminal voltage is above 3.24 VDC except terminators may source current when the voltage is above 3.24 VDC in applications where the bus is less than 0.3 m;

Figure 1.12 Single-Ended SCSI termination circuit-1

# (2) Driver and receiver

For the interface signal driver, an open-collector or tri-state buffer that satisfies the following output characteristics is used. All signals are negative logic (true = "L").

The receiver and non-driver of the SCSI device under the power-on state should satisfy the following input characteristics on each signal.

| Driver Type      | Value | Min | Max  | Notes     |

|------------------|-------|-----|------|-----------|

| Passive Negation | Vol   | 0.0 | 0.5  | @IoL=48mA |

|                  | Vон   | 2.5 | 5.25 |           |

| Active Negation  | Vol   | 0.0 | 0.5  | @IoL=48mA |

|                  | Vон   | 2.5 | 3.7  |           |

Table 1.6Output characteristic

| Maximum<br>transfer mode |                                | Min  | Max | Notes       |

|--------------------------|--------------------------------|------|-----|-------------|

|                          | Vil [VDC]                      | -    | 0.8 |             |

|                          | Vih [VDC]                      | 2.0  | -   |             |

| Fast-5                   | IIL [mA]                       | -0.4 | 0.0 | @VI= 0.5VDC |

|                          | Ін [mA]                        | 0.0  | 0.1 | @VI= 2.7VDC |

|                          | Minimum input hysteresis [VDC] | 0.2  | -   |             |

|                          | Vil [VDC]                      | -    | 0.8 |             |

|                          | Vih [VDC]                      | 2.0  | -   | @VI= 0.5VDC |

| Fast-10                  | Iπ [μA]                        | -20  | 20  | @VI= 2.7VDC |

|                          | Ін [μА]                        | -20  | 20  |             |

|                          | Minimum input hysteresis [VDC] | 0.3  | -   |             |

|                          | Vil [VDC]                      | -    | 1.0 |             |

|                          | Vih [VDC]                      | 1.9  | -   |             |

| Fast-20                  | Ιπ [μA]                        | -20  | 20  | @VI= 0.5VDC |

|                          | Ін [µА]                        | -20  | 20  | @VI= 2.7VDC |

|                          | Minimum input hysteresis [VDC] | 0.3  | -   |             |

Table 1.7Input characteristic

# Note:

The SCSI device under the power-off state should satisfy the characteristics of  $I_{IL}$  and  $I_{IH}$ .

```

[Recommended circuit example]

Driver:MB463 (Fujitsu) or SN7438 (TI) (Open-collector NAND gate)

Receiver:SN74LS240 or SN74LS19 (TI) (Shumitt trigger input inverter)

```

# 1.4.2 Low-Voltage Differential type

(1) Termination circuit

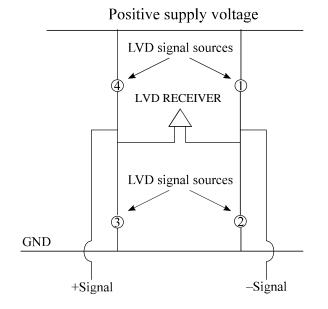

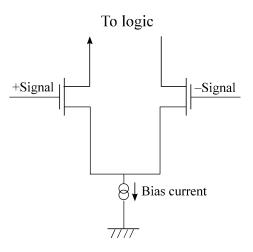

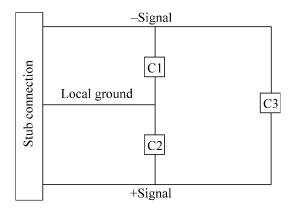

All signals except for GROUND and TERMPWR should be terminated at both ends of the bus. Each signal should be terminated. Figure 1.14 shows the termination circuit.

Figure 1.14 LVD SCSI termination circuit

## (2) DIFFSENS

#### a) DIFFSENS driver

The LVD DIFFSENS driver sets a voltage level on the DIFFSENS line that uniquely defines a LVD transmission mode. LVD terminators and multimode terminators shall provide a LVD DIFFSENS driver according to the specifications in Table 1.8.

| Value                                                 | Max. | Nominal | Min | Notes                                                                                                   |

|-------------------------------------------------------|------|---------|-----|---------------------------------------------------------------------------------------------------------|

| $V_0$ [V] when $I_0=0$<br>(shorted to ground) to 5mA  | 1.4  | 1.3     | 1.2 |                                                                                                         |

| I <sub>OS</sub> [mA]                                  | 15   | 5       | -   | With TERMPWR at operational levels and $V_0=0$ .                                                        |

| Input current DC (µA)                                 | 10   | -       | -   | With terminator disabled.                                                                               |

| Input sink current D.C. (µA) at V <sub>0</sub> =2.75V | 200  | -       | 20  | Required to prevent the line from<br>floating and to ensure the HVD<br>DIFFSENS driver dominate the LVD |

Table 1.8 LVD DIFFSENS driver specifications

## b) DIFFSENS receiver

LVD SCSI devices shall incorporate a LVD DIFFSENS receiver that detects the voltage level on the DIFFSENS line for purposes of informing the device of the transmission mode being used by the bus. The LVD DIFFSENS receiver shall be capable of detecting SE and LVD SCSI devices. Table 1.9 define the receiver input levels for each of the two modes.

| V <sub>IN</sub> range | Sensed differential drive type |

|-----------------------|--------------------------------|

| $-0.35 \sim +0.5V$    | SE                             |

| $+0.7 \sim +1.9 V$    | LVD                            |

The input resistance requirement is for purposes of providing ground reference if no DIFFSENS drivers are connected to the bus and to ensure that the DIFFSENS receivers do not load the DIFFSENS drivers excessively and to ensure that SE mode is detected.

Devices shall not allow the signal drivers to leave the high impedance state during initial power on until both of the following conditions are satisfied:

a) The device is capable of logical operation for at least 100 ms, and

#### Notes:

The 100 ms delay allows time for the DIFFSENS pin to connect after the initial power connection (in the case of insertion of a device into an active system), or allows time for the power distribution system to settle.

b) The DIFFSENS mode detected has remained stable for an additional 100 ms after a) is achieved.

A device shall not change its present signal driver or receiver mode based on the DIFFSENS voltage level unless a new mode is sensed continuously for at least 100 ms.

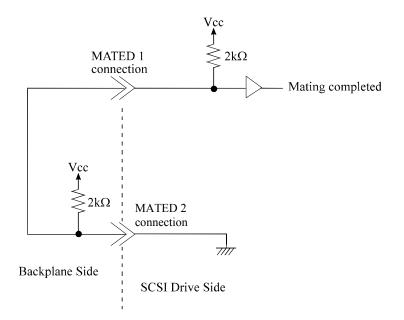

#### (3) MATED Signals

If MATED 1 and MATED 2 signals are not mated then one or more short pins are not mated. If MATED 1 and MATED 2 signals are mated then the mated condition of the short pins is indeterminate. The MATED 1 and MATED 2 signals may indicate to the SCSI device that the SCSI device is seated in an SCA-2 connector and it may begin power on processing. The signal requirements are indicated below, but may be met by the circuit.

a) MATED 2/Drive Side

The signal is attached to signal ground on the SCSI device side.

b) MATED 2/Backplane Side

The signal is attached either directly or through optional logic in such a manner that the MATED 1 signal is held to a ground level when the MATED 2 connection is completed. The SCSI device shall sink no more than 100 mA to ground through the MATED 2 pin if optional logic is used.

c) MATED 1/Drive Side

The MATED 1 signal shall be sensed by the SCSI device. When the MATED 1 connection is determined to be at a ground level, the SCSI device may assume that the SCSI device has been partially mated. Assuming the mating process continues uninterrupted until competition, including sensing of the SCSI ID Selection signals and the motor start controls, then normal power on procedures may begin 250 msec after the MATED 1 signal is observed to transition to the ground level. When the MATED 1 connection is determined to be at the open level, the SCSI device is not mated. The MATED 1 signal is tied up to a TTL positive level when the SCSI device is not installed. If the SCSI device is mated and operating, it may optionally detect the open level of MATED 1 as an indication that the SCSI device is partially unmated and may be about to be removed. If the SCSI device supports detection of the open level of MATED 1 to prepare itself for power removal or for physical removal from the enclosure, the detection shall occur within 1 second from the time that the Mated 1 open level occurs at the SCSI device.

## (4) MATED 1/Backplane Side

The signal shall be held to a ground level when the MATED 2 connection is completed. The MATED 1 signal shall be held to the open level when the MATED 2 connection is not completed.

Figure 1.15 Circuit for mated indications

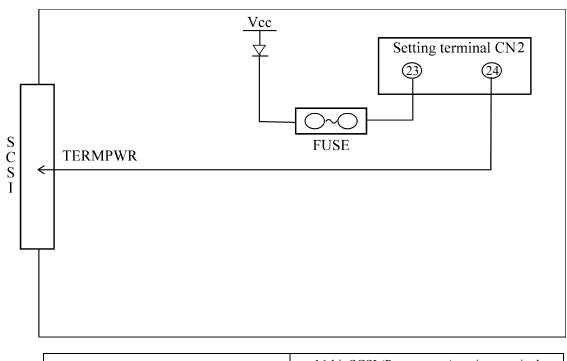

## 1.4.3 Internal terminal resistor and power supply for terminating resistor

The TERMPWR signal of the interface connector supplies the power to the terminating resistor circuit connected to both ends of the cable. To attach a terminating resistor to an external SCSI device or to cut the power of SCSI device having a terminator, the terminator power must be supplied to the TERMPWR line from any of SCSI devices of the bus. The SCSI device (such as a host adapter) which always operates as the INIT should supply the power. The terminating resistor power shall be supplied to the TERMPWR line through a diode to prevent a reverse current.

Table 1.10 lists the requirements for terminating the resistor power supply (Vterm).

| Terminator Power                        | Terminator Type |      |      |                                   |  |

|-----------------------------------------|-----------------|------|------|-----------------------------------|--|

|                                         | SE (P Cable)    |      |      | SE and LVD<br>type<br>(Multimode) |  |

| Characteristics 0.2V dropout regulator  |                 |      | LVD  |                                   |  |

| I <sub>min</sub> (A)@V <sub>min</sub>   | 0.6             | 0.6  | 0.5  | 0.65                              |  |

| $V_{min}(V)@I_{min}$                    | 2.7             | 4.0  | 3.0  | 3.0                               |  |

| V <sub>max</sub> (V)@ all<br>conditions | 5.25            | 5.25 | 5.25 | 5.25                              |  |

Table 1.10

Requirements for terminating resistor power supply

Figure 1.16 shows the configuration of a SCSI terminating resistor circuit. The circuit shall be set in either mode (by the CN2 setup pin) depending on the IDD system requirements.

|                                  | 16-bit SCSI (P-connector) setting terminal<br>CN2 23-24pin |

|----------------------------------|------------------------------------------------------------|

| Supply TERMPWR to SCSI Bus       | Short                                                      |

| Don't supply TERMPWR to SCSI Bus | Open                                                       |

# Figure 1.16 16-bit SCSI (not SCA2) terminating resistor circuit

#### Notes:

All series have no internal terminator circuit. If the terminator circuit is needed, you should add the external circuit on your system.

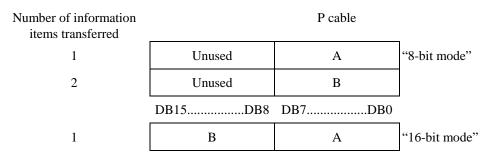

# 1.4.4 Usage in 8-bit/16-bit transfer mode

When the IDD is used as 8-bit SCSI device, it is connected terminating resistor circuit to upper 8bit and parity (DB08 to DB15 and DBP1) or short set up pin (CN2 13-14). When the IDD is used as 16-bit SCSI device, leave the set up pin Jumper setting "8/16" open. Table 1.11 shows the guide. Jumper setting is available only for MP series.

| Transfer mode | Jumper setting "8/16" | DB08 to DB15 and DBP1            |

|---------------|-----------------------|----------------------------------|

|               | Short                 | Don't care.                      |

| 8bit (narrow) | Open                  | Should be terminated externally. |

| 16bit (wide)  | Should be opened      | Don't care.                      |

Table 1.11

Setting set up pin, 16-bit (wide)/8-bit (narrow) mode

## 1.4.5 Signal driving conditions

#### (1) Signal status value

Table 1.12 shows the correspondence between the input interface signal level at the receiving end and its logic state.

|                                    | Single-ended t                    | ype signal state            | LVD type signal<br>state    |  |

|------------------------------------|-----------------------------------|-----------------------------|-----------------------------|--|

| Logic state                        | Asynchronous, Fast-<br>5, Fast-10 | Fast-20                     |                             |  |

| True, "1", or<br>asserted          | Low (less than 0.8 VDC)           | Low (less than 1.0 VDC)     | Low (-3.6 to -0.030<br>VDC) |  |

| False, "0", negated<br>or released | High (more than 2.0 VDC)          | High (more than 1.9<br>VDC) | High (0.030 to 3.6<br>VDC)  |  |

Table 1.12Signal status at receiving end

## (2) Signal driving method

Two driving methods are available: "OR-tied" type and "non-OR-tied" type as indicated in Table 1.13.

| Table 1.13 | Signal driving | method |

|------------|----------------|--------|

|------------|----------------|--------|

| Driving method<br>Signal status | "OR-tied" type                                                                                                     | "non-OR-tied" type                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| False (*1)                      | No SCSI device drives a signal.<br>The signal becomes false when<br>the terminating resistor circuit<br>is biased. | A particular SCSI device drives<br>the signal false. Otherwise, no<br>SCSI device drives the signal. |

| True                            | A SCSI device dri                                                                                                  | ives the signal true                                                                                 |

\*1 In this manual, the signal is said to be false if one of the following conditions is satisfied.

- 1. The signal is actually driven by a SCSI device to become false (non-OR-tied type).

- 2. No SCSI device is driving the signal (OR-tied type or non-OR-tied type).

If the BSY, SEL and RST signals may be driven by two or more SCSI devices simultaneously in the interface operating sequence, they must be driven in the OR-tied method. All signals except for SEL, BSY, RST and DB(P\_CRCA, P1) are not driven by multiple SCSI devices simultaneously. However, the DBP signals must be driven false in the ARBITRATION phase. All signals driven in OR-tied and non-OR-tied method can be mixed on the same signal line of SCSI bus except for BSY, SEL and RST signals.

## (3) Signal sources

Table 1.14 lists SCSI device types (or signal sources) which can drive signals in each interface operating phase.

|                 | BSY | SEL | I/O,<br>REQ,<br>C/D,<br>MSG | ACK,<br>ATN | DB7-0 | DB15-8,<br>DBP1 | P_CRCA | RST |

|-----------------|-----|-----|-----------------------------|-------------|-------|-----------------|--------|-----|

| BUS FREE        | Ν   | Ν   | N                           | Ν           | N     | Ν               | Ν      | А   |

| ARBITRATION     | Α   | W   | N                           | Ν           | ID    | ID              | ID     | А   |

| QAS ARBITRATION | PT  | W   | Ν                           | N           | ID    | ID              | ID     | ID  |

| SELECTION       | I&T | Ι   | N                           | Ι           | Ι     | Ι               | Ι      | Α   |

| RESELECTION     | I&T | Т   | Т                           | Ι           | Т     | Т               | Т      | А   |

| COMMAND         | Т   | Ν   | Т                           | Ι           | Ι     | Ν               | Ι      | Α   |

| ST DATA IN      | Т   | Ν   | Т                           | Ι           | Т     | Т               | Т      | Α   |

| ST DATA OUT     | Т   | Ν   | Т                           | Ι           | Ι     | Ι               | Ι      | А   |

| DT DATA IN      | Т   | Ν   | Т                           | Ι           | Т     | Т               | Т      | Α   |

| DT DATA OUT     | Т   | Ν   | Т                           | Ι           | Ι     | Ι               | Т      | Α   |

| STATUS          | Т   | N   | Т                           | Ι           | Т     | Ν               | Т      | Α   |

| MESSAGE IN      | Т   | Ν   | Т                           | Ι           | Т     | Ν               | Т      | А   |

| MESSAGE OUT     | Т   | Ν   | Т                           | Ι           | Ι     | Ν               | Ι      | А   |

Table 1.14Bus phases and signal sources

- A: Any SCSI device can drive the signal. Also, two or more SCSI devices may drive the signal simultaneously.

- I: Only the INIT SCSI device drives the signal.

- I&T: The INIT and TARG SCSI devices drive the signal in the interface operating sequence. INIT, TARG or both can drive this signal according to the interface sequence.

- I or T: The INIT or TARG SCSI device (or both devices) may drive the signal depending on the I/O signal status and bus width.

- ID: Each SCSI device which is actively arbitrating the bus drives a unique data bit (SCSI ID). The parity bit may be undriven or driven to the true state, but must never be driven to the false state.

- N: Not be driven by any SCSI device.

- T: Only the TARG SCSI device drives the signal.

- W: Only a single SCSI device selected through arbitration drives the signal.

# 1.5 Timing Rule

# 1.5.1 Timing value

Table 1.15, 16, 17 give the timing required for operations on the SCSI bus.

|    | Timing description           | Туре | Timing values |

|----|------------------------------|------|---------------|

| 1  | Arbitration delay            | Min  | 2.4 μs        |

| 2  | Bus clear delay              | Max  | 800 ns        |

| 3  | Bus free delay               | Min  | 800 ns        |

| 4  | Bus set delay                | Max  | 1.6 µs        |

| 5  | Bus settle delay             | Min  | 400 ns        |

| 6  | Cable skew (1)               | Max  | 4 ns          |

| 7  | Data release delay           | Max  | 400 ns        |

| 8  | DIFFSENS voltage filter time | Min  | 100 ms        |

| 9  | Physical disconnection delay | Min  | 200 µs        |

| 10 | Power on to selection (2)    | Max  | 10 s          |

| 11 | QAS arbitration delay        | Min  | 1000 ns       |

| 12 | QAS assertion delay          | Max  | 200 ns        |

| 13 | QAS release delay            | Max  | 200 ns        |

| 14 | QAS non-DATA phase REQ(ACK)  | Min  | 50 ns         |

|    | peiod                        |      |               |

| 15 | Reset delay                  | Min  | 200 ns        |

| 16 | Reset hold time              | Min  | 25 μs         |

Table 1.15

SCSI bus control timing values

**Note:** (1) Cable Skew is measured at each device connection with the transmitted skew subtracted from the received skew. (2) This is a recommended time. It is not mandatory.

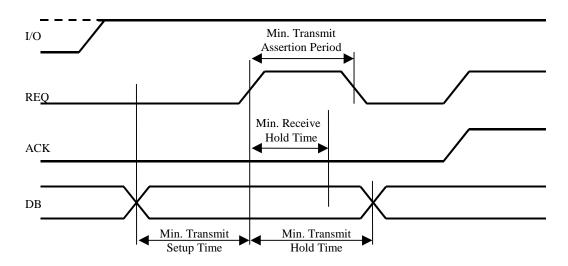

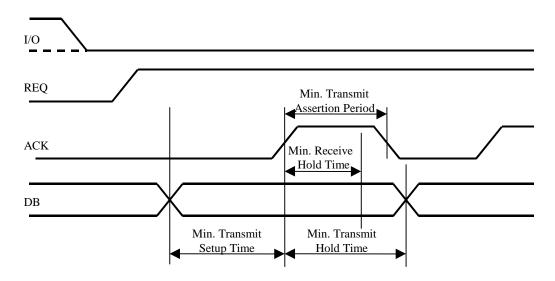

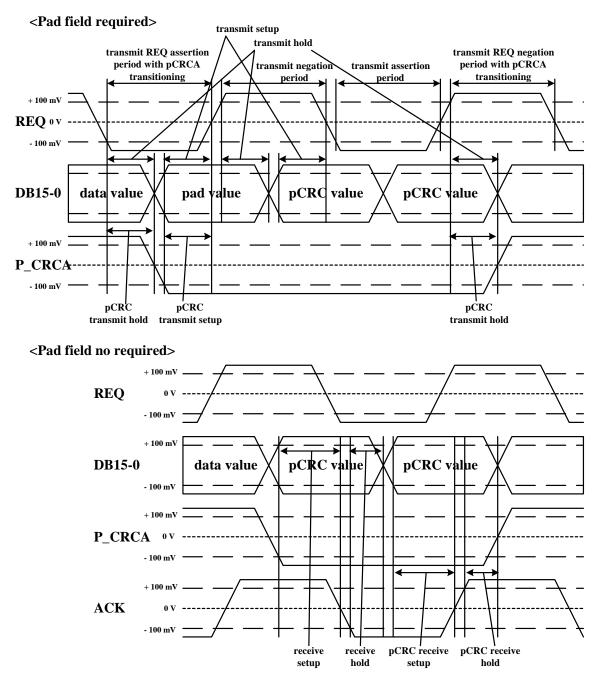

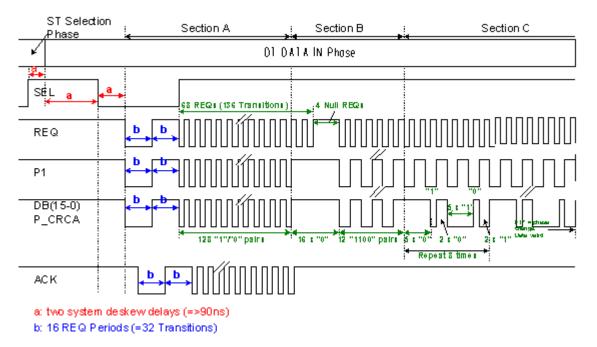

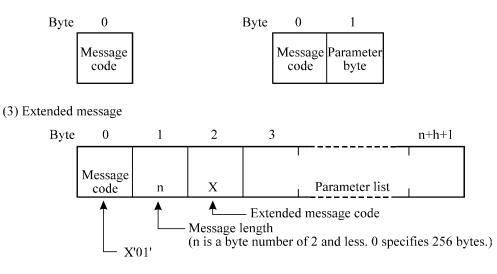

|    | Timing description                  |      | Timing values [ns] (5) |        |         |         |         |  |